Memory Partitioning and Slack Scheduling Boost Performance in Safety-Critical Applications | Electronic Design

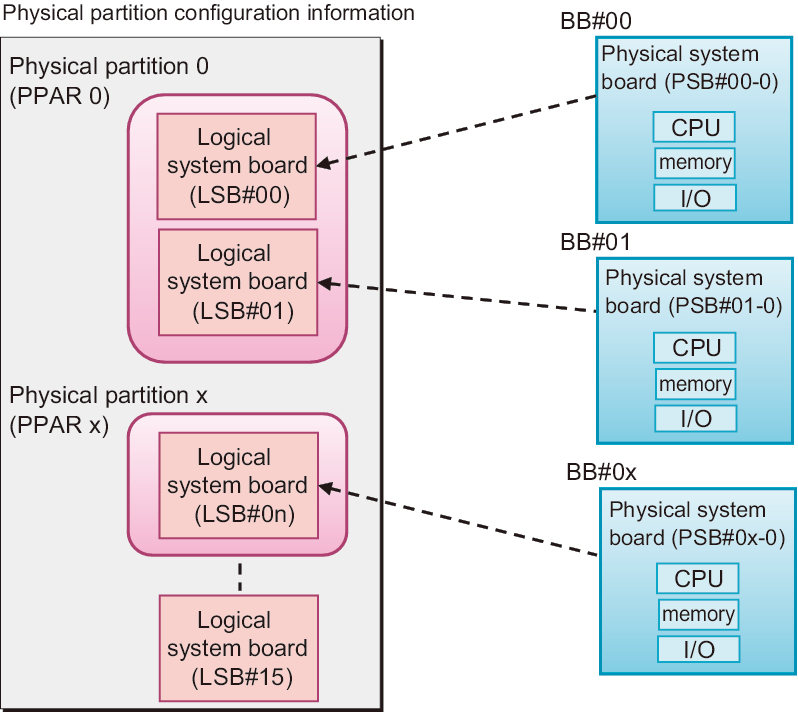

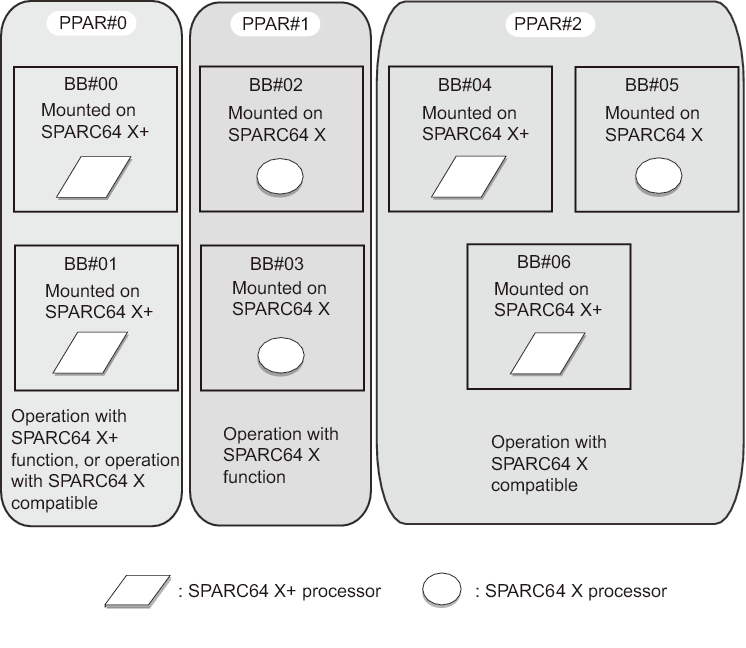

Understanding Micro partitioning , WHAT IS MICROPARTITIONING , WHAT IS SHARED CPU , POWER VIRTUALIZATION CPU ASSIGNMENT | TECH RECEPIES FOR IT ADMINS

Oracle VM hard partitioning – potential licensing and performance issues | Eric Steed – Technology Evangelist

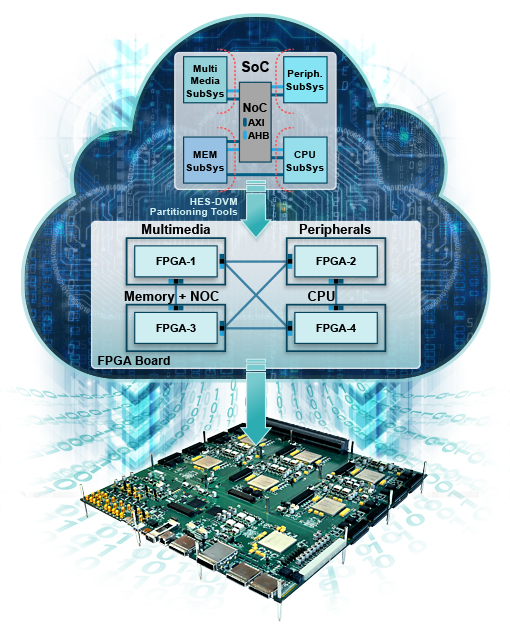

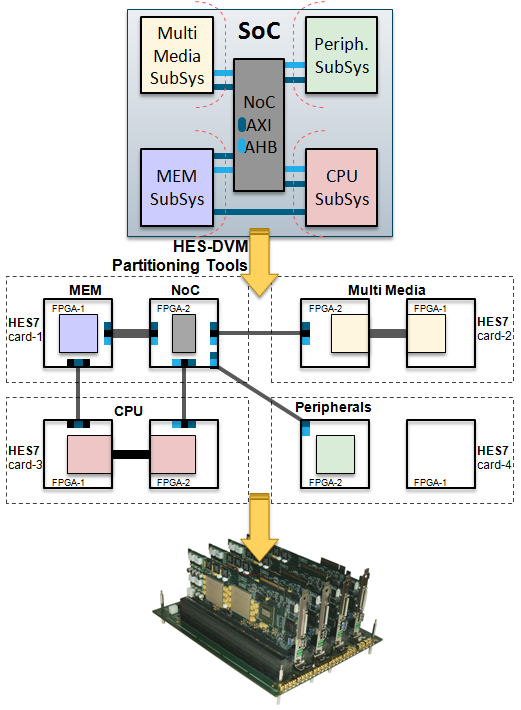

Aldec solves ASIC design partitioning challenges with HES-DVM Proto mode - 2017-09-11 - Newsroom - Company - Aldec

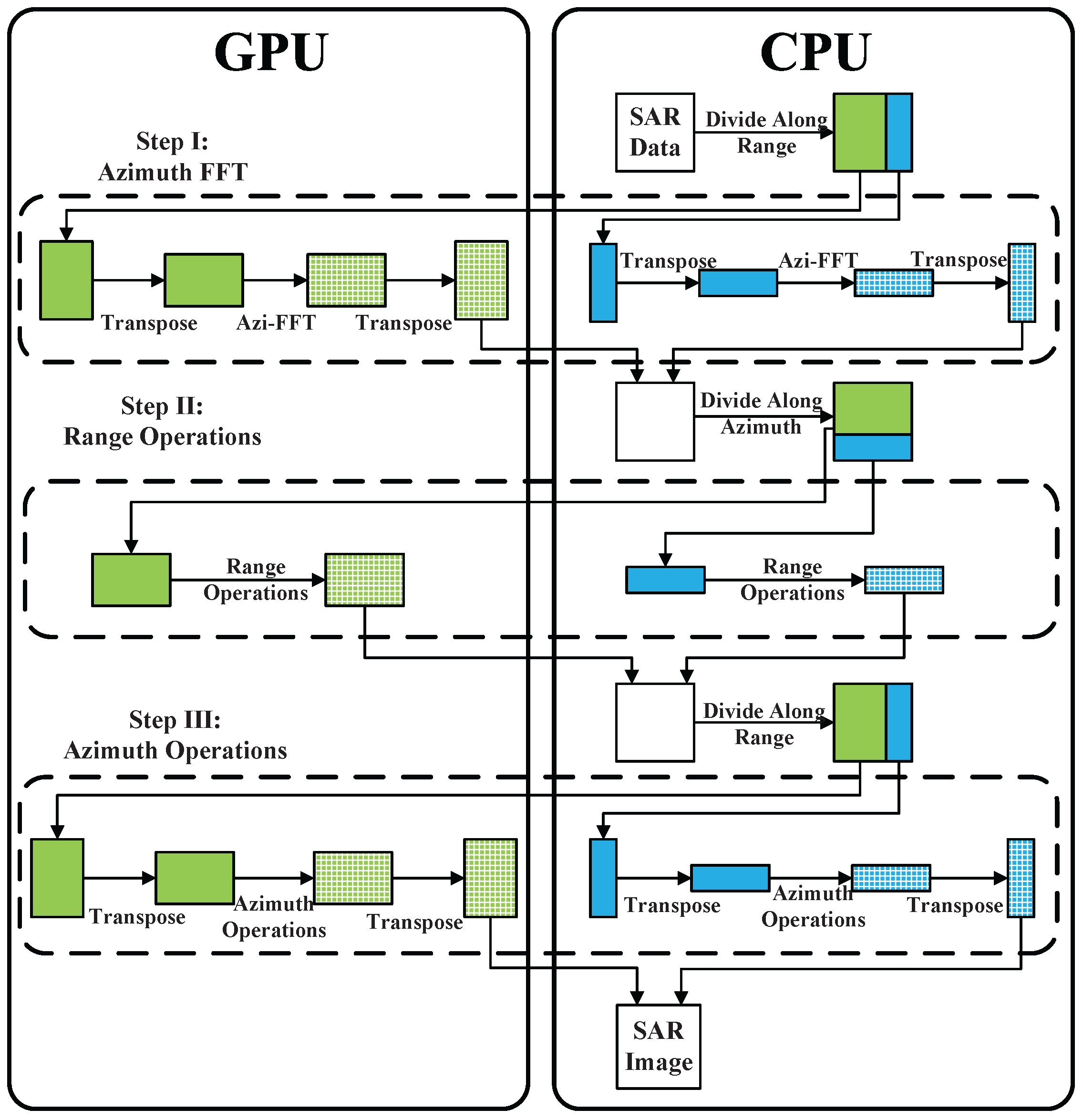

Sensors | Free Full-Text | Accelerating Spaceborne SAR Imaging Using Multiple CPU/GPU Deep Collaborative Computing

Sparse matrix partitioning for optimizing SpMV on CPU-GPU heterogeneous platforms - Akrem Benatia, Weixing Ji, Yizhuo Wang, Feng Shi, 2020

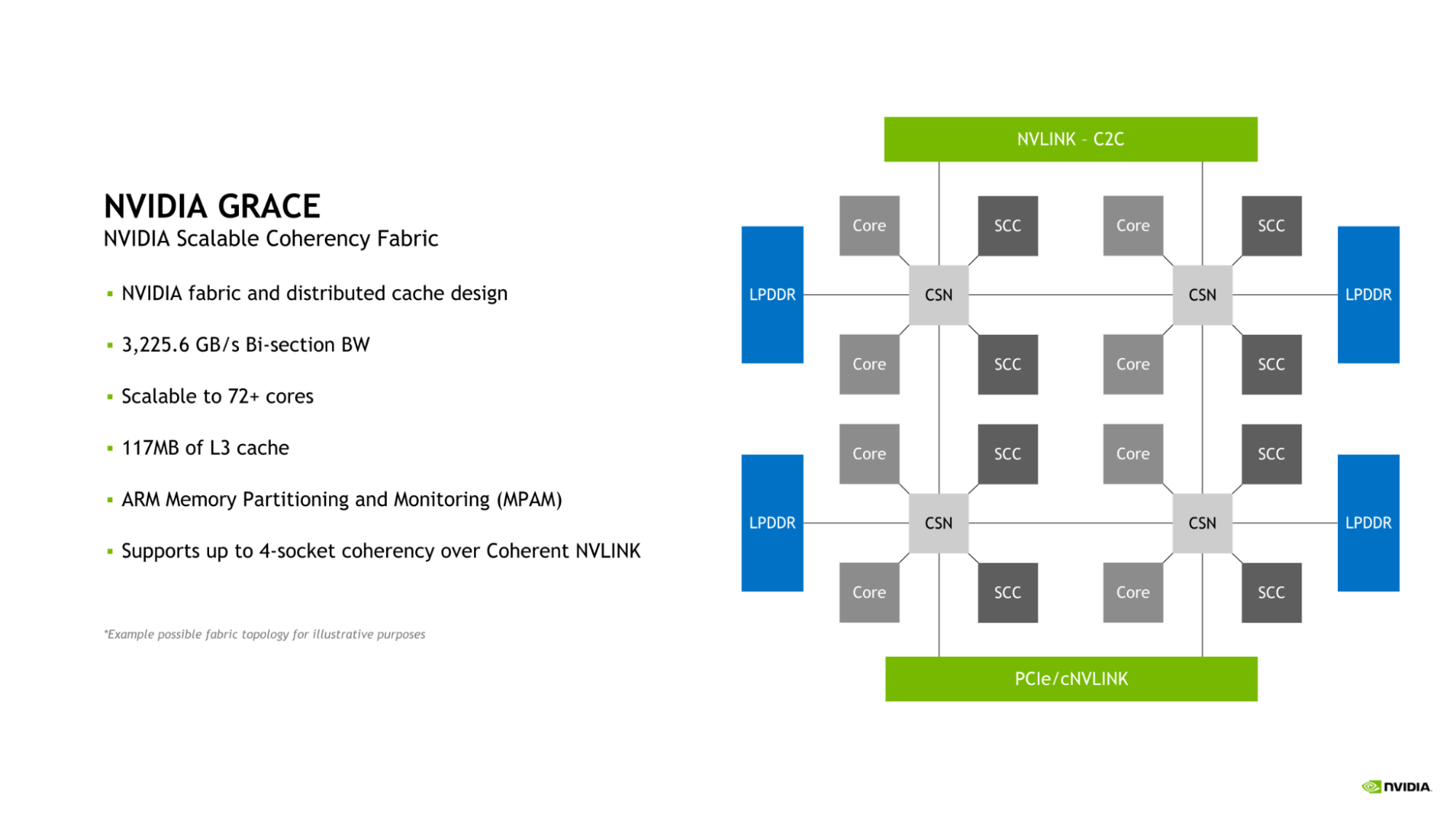

Inside NVIDIA Grace CPU: NVIDIA Amps Up Superchip Engineering for HPC and AI | NVIDIA Technical Blog

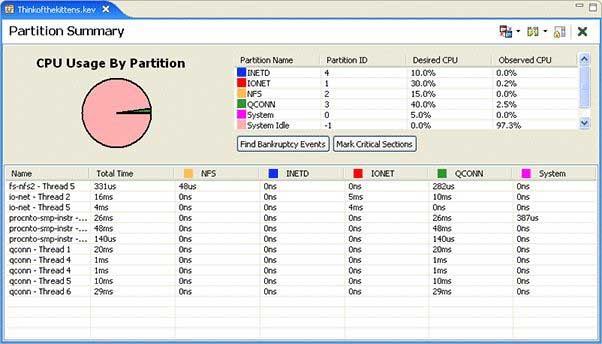

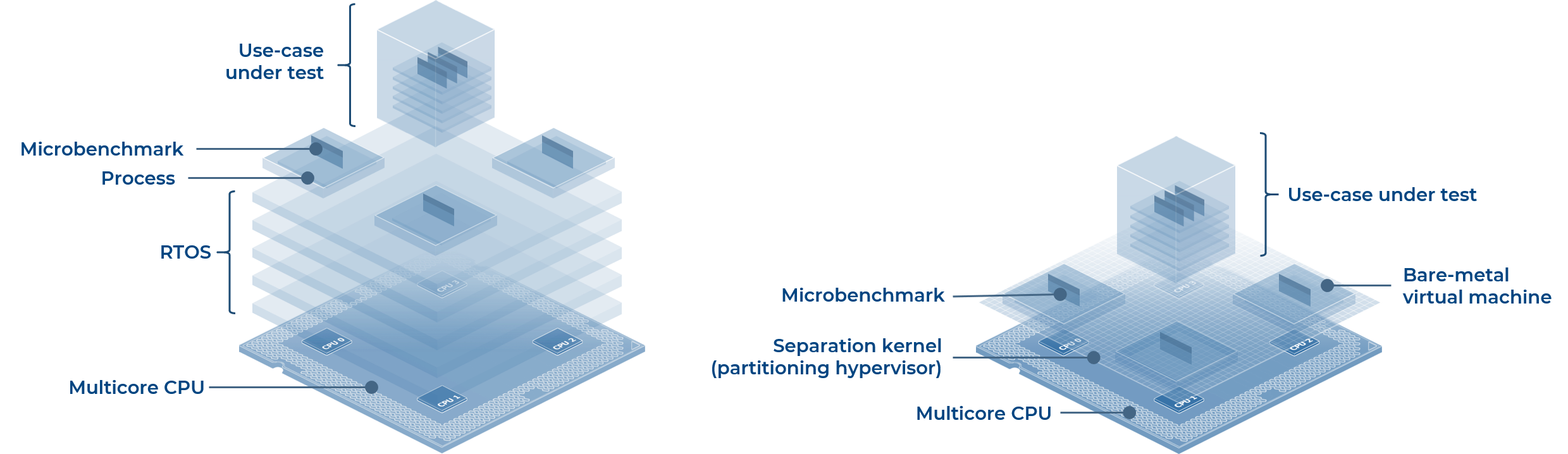

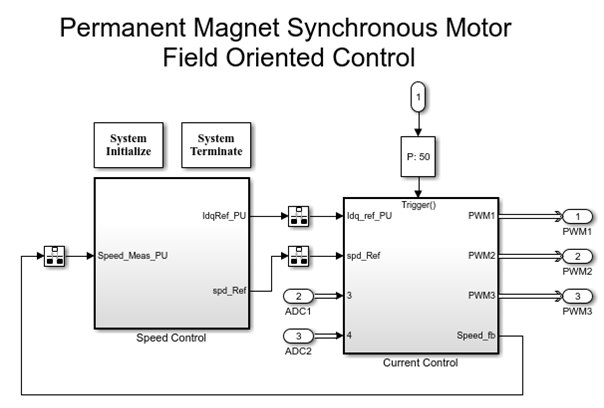

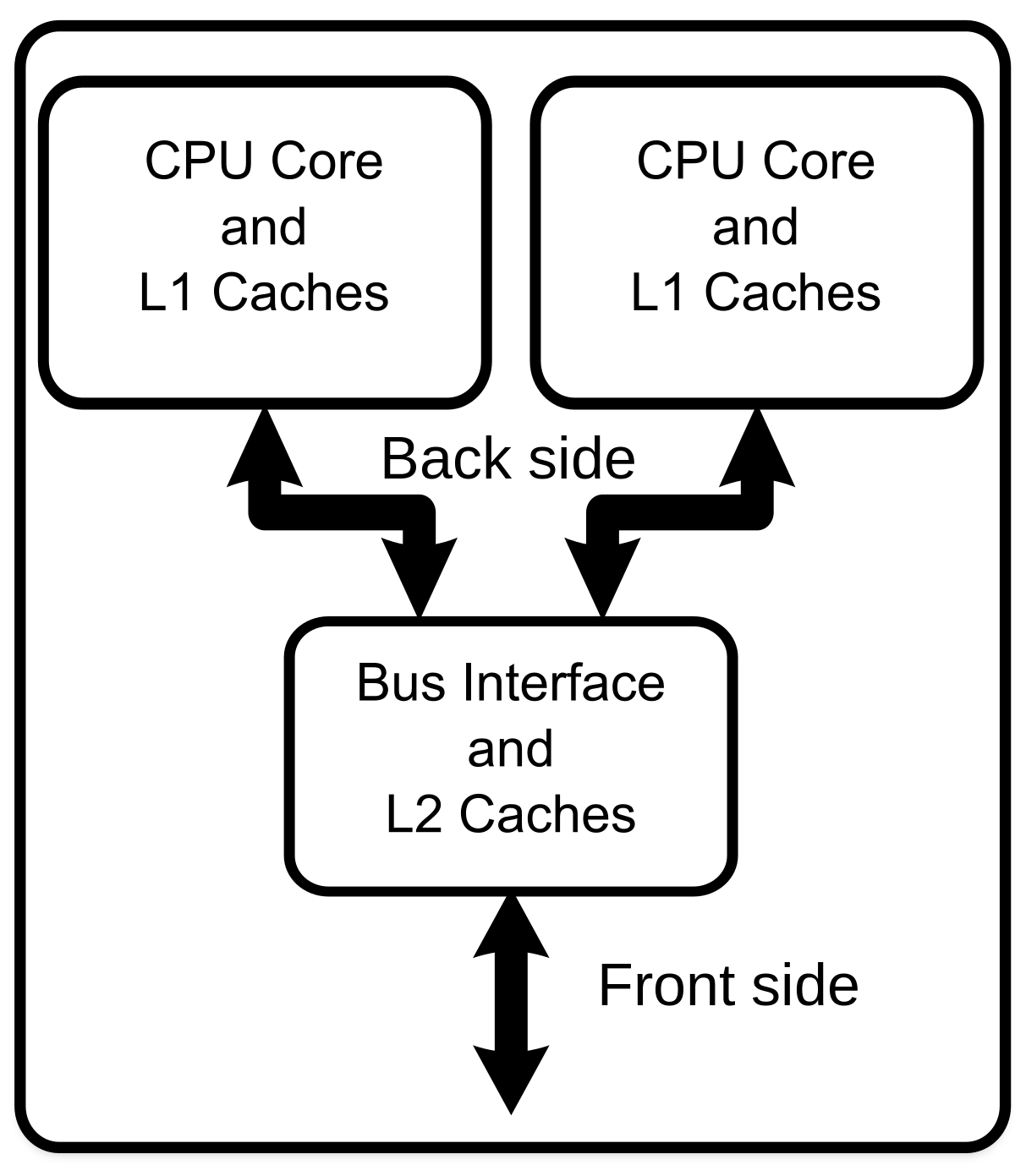

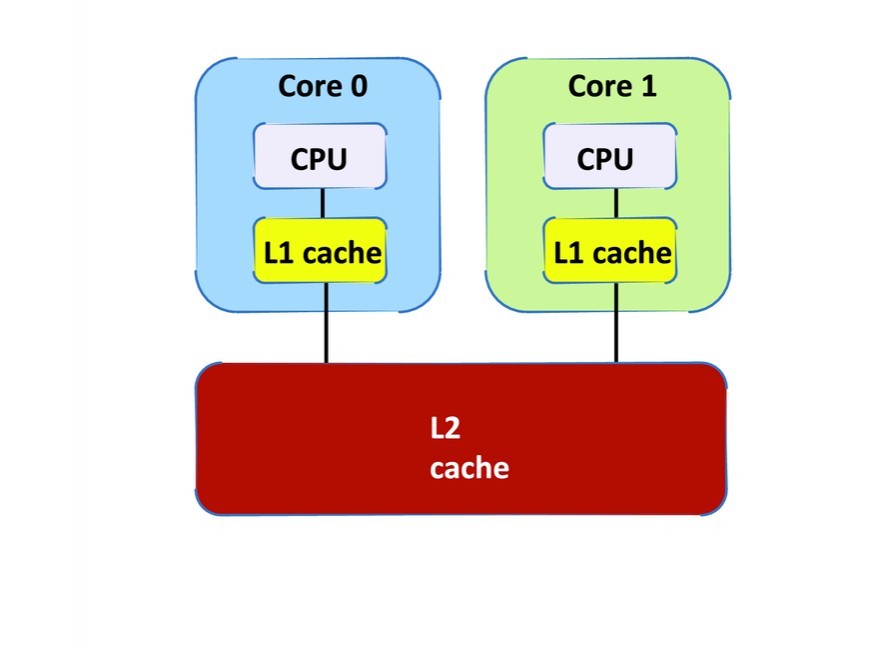

Cache partitioning increases CPU utilization for safety-critical multicore applications - Military Embedded Systems

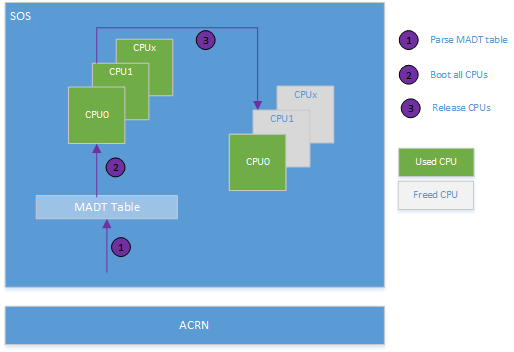

Cache partitioning increases CPU utilization for safety-critical multicore applications - Military Embedded Systems